博客

ESD/EOS管控對IC封裝測試端的行業價值產出

||

1. IC封裝測試階段是IC最ESD最為敏感的

1>IC中的晶片(Die)從Wafer中分切出來,失去了原有Wafer級的ESD保護;

2>晶片在進行封裝中,與封裝體會發生必然的ESD事件;

3>IC封裝后的功能測試,易于遭受ESD與EOS的雙重侵襲。

2. 部分業內IC封裝測試階段的ESD/EOS解決實例

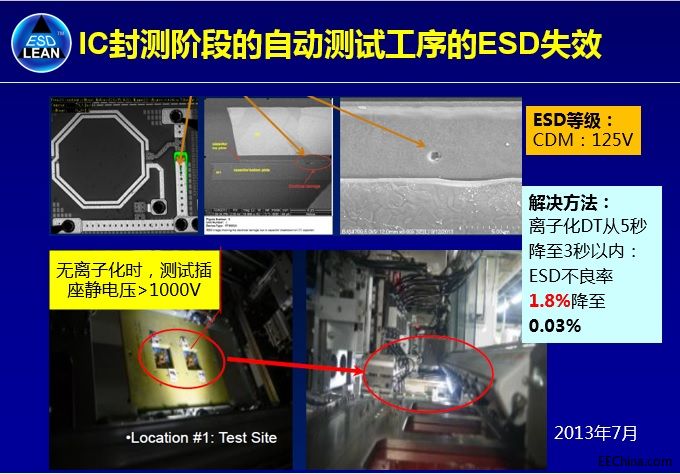

2.1 IC在自動測試中的ESD損壞解決

ESD背景:IC封測廠收到客戶的IC(Low Pass Filter,低通濾波器)品質(Insertion Loss Failure,插入損失失效)投訴,IC封測廠追溯分析發現來自于單一測試機的ESD不良(10#管腳對地擊穿)達1.8%。

IC ESD損壞分析與解決:此IC ESD敏感度較高(CDM耐壓值僅為125V),IC在自動裝入測試機測試插座中產生高靜電,在裝入插座中即發生CDM放電。ESD解決措施為調整IC裝載處的離子化安裝,將衰減時間縮短是3秒以內,IC的ESD不良率降至0.03%以下。

1>IC中的晶片(Die)從Wafer中分切出來,失去了原有Wafer級的ESD保護;

2>晶片在進行封裝中,與封裝體會發生必然的ESD事件;

3>IC封裝后的功能測試,易于遭受ESD與EOS的雙重侵襲。

2. 部分業內IC封裝測試階段的ESD/EOS解決實例

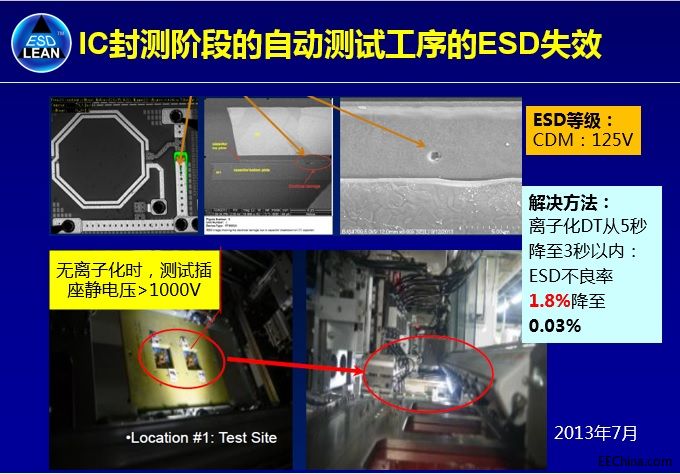

2.1 IC在自動測試中的ESD損壞解決

ESD背景:IC封測廠收到客戶的IC(Low Pass Filter,低通濾波器)品質(Insertion Loss Failure,插入損失失效)投訴,IC封測廠追溯分析發現來自于單一測試機的ESD不良(10#管腳對地擊穿)達1.8%。

IC ESD損壞分析與解決:此IC ESD敏感度較高(CDM耐壓值僅為125V),IC在自動裝入測試機測試插座中產生高靜電,在裝入插座中即發生CDM放電。ESD解決措施為調整IC裝載處的離子化安裝,將衰減時間縮短是3秒以內,IC的ESD不良率降至0.03%以下。