博客

于爭《電源完整性設計詳解》學習總結

||

短短的十幾頁說明將電源完整性說明的通透無比,對比以往所看的教材都只是在表面說明一下就一筆帶過,這樣事是而非的解答并沒有起到多大的作用,反而更容易引起其他方面的疑惑。

現將學習心得總結如下:

一:電源系統噪聲余量分析

比如芯片正常工作電壓范圍為 3.13V 到 3.47V 之間,穩壓芯片標稱輸出 3.3V。安裝到電路板上后,穩壓芯片輸出3.36V。那么容許電壓變化范圍為 3.47-3.36=0.11V=110mV。穩壓芯片輸出精度±1%,即±3.363*1%=±33.6 mV。電源噪聲余量為 110-33.6=76.4 mV

注意四個問題:

第一,穩壓芯片輸出電壓能精確的定在 3.3V 么?外圍器件如電阻電容電感的參數也不是精確的,這對穩壓芯片的輸出電壓有影響,所以這里用了 3.36V 這個值。在安裝到電路板上之前,你不可能預測到準確的輸出電壓值。

第二,工作環境是否符合穩壓芯片手冊上的推薦環境?器件老化后參數還會和芯片手冊上的一致么?

第三,負載情況怎樣?這對穩壓芯片的輸出電壓也有影響。

第四,電源噪聲最終會影響到信號質量。而信號上的噪聲來源不僅僅是電源噪聲,反射串擾等信號完整性問題也會在信號上疊加噪聲,不能把所有噪聲余量都分配給電源系統。所以,在設計電源噪聲余量的時候要留有余地。

第一,穩壓芯片輸出電壓能精確的定在 3.3V 么?外圍器件如電阻電容電感的參數也不是精確的,這對穩壓芯片的輸出電壓有影響,所以這里用了 3.36V 這個值。在安裝到電路板上之前,你不可能預測到準確的輸出電壓值。

第二,工作環境是否符合穩壓芯片手冊上的推薦環境?器件老化后參數還會和芯片手冊上的一致么?

第三,負載情況怎樣?這對穩壓芯片的輸出電壓也有影響。

第四,電源噪聲最終會影響到信號質量。而信號上的噪聲來源不僅僅是電源噪聲,反射串擾等信號完整性問題也會在信號上疊加噪聲,不能把所有噪聲余量都分配給電源系統。所以,在設計電源噪聲余量的時候要留有余地。

二:電源噪聲是如何產生的?

第一,穩壓電源芯片本身的輸出并不是恒定的,會有一定的波紋。

第二,穩壓電源無法實時響應負載對于電流需求的快速變化。

第三,負載瞬態電流在電源路徑阻抗和地路徑阻抗上產生的壓降。

三:電容退耦的兩種解釋

1. 從儲能的角度來說明電容退耦原理

大部分教材都是以此來解說的,特別是對于板級電源的退耦大電容。即認為當負載電流突然變化時,電源輸出反應時間沒有負載所需的電流變化快而造成電壓下降,此時大電容兩端電壓發生變化而開始放電來補充負載所需的電流變化值。從以上來講即退耦電容作為一個儲能期間來滿足負載的電流變化。

這樣理解簡單易懂,但是是乎總是缺少點什么,并沒有從電源完整性的原理上加以闡述清楚。

2. 從阻抗的角度來理解退耦原理

電源可以如下公式表述:ΔV=ZΔI

電源完整性的實質即是負載電流如何變化時,電壓變化值均要在很小的范圍之內,為了滿足這個要求就必須使電源動態阻抗很小。我們是通過去耦電容來達到這一要求的,因此從等效的角度出發,可以說去耦電容降低了電源系統的阻抗。另一方面,從電路原理的角度來說,可得到同樣結論。電容對于交流信號呈現低阻抗特性,因此加入電容,實際上也確實降低了電源系統的交流阻抗。

這里我們可以得出電源完整性實質即是使電源使阻抗最小。

補充:電源回路中經常會加入磁珠或電感進行濾波處理,但這會不會增加電源路徑阻抗呢?

本人是這樣理解。

PCB中通常是模擬和數字混合電路,因為現代數字IC信號上升或下降變化均為納秒級,所以在大量IO口或時鐘信號線變化時有眾多信號上升或下降所產生數量龐大的高次諧波,同時電位變化將產生不斷變化的電流,其流過電線以及印刷電路板上的電源和電子器件間的布線與層面,產生出電壓變化:

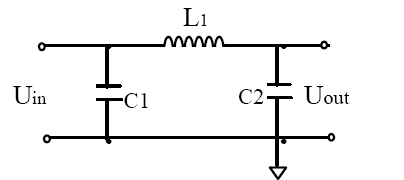

其中,C1 為輸入側的輸入電容,L 為輸入電感,C2 為П型濾波電路的輸出側 電容;C1 的主要目的是為了限制上電瞬間的電壓上升率,并濾除輸入側電路由電源引入的紋波,因此,C1一般是由直流電容及交流電容組成的并聯電容組,其中直流電容的主要作用是去除電容中的紋波,而交流電容的主要作用是為了去耦.從參數及器件選擇上,輸入側一般選取鉭電容,去耦電容的值為0.01uf ~1uf 之間,針式或貼片均可,但從生產工藝的角度,則以選取貼片為佳,推薦的參數為直流電容10uf,交流電容0.1uf。 電感的作用為抑制電流變化率,電感越大,抑制效果越好,但同時電感太大時的上電特性不好,上電及下電時,電感兩端會產生反電勢,這樣會對后面的負載產生影響,故參數不宜過大,因而推薦的參數為10uH.輸出側的電容不僅要完成去耦及濾紋波的作用,而且還須維持濾波后電平不受電感反電勢的影響,兼顧考慮板內負載大小及板內其他去耦電容的數量,推薦參 數為直流電容10uf,交流電0.01~1uf。

本文來自CSDN博客,轉載請標明出處:http://blog.csdn.net/yd4330152763132/archive/2010/10/25/5964757.aspx