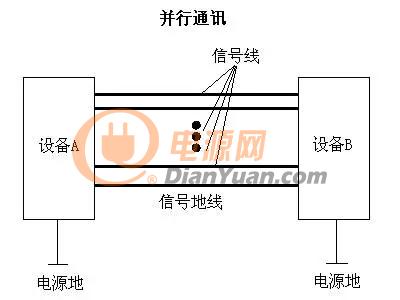

并行通訊通常可以一次傳送8bit、16bit、32bit甚至更高的位數(shù),相應(yīng)地就需要8根、16根、32根信號(hào)線,同時(shí)需要加入更多的信號(hào)地線。比如傳統(tǒng)的PATA線路有40根線,其中有16根信號(hào)線和7根信號(hào)地線,其他為各種控制線,一次可以傳送2Byte的數(shù)據(jù)。并行通訊中,數(shù)據(jù)信號(hào)中無法攜帶時(shí)鐘信息,為了保證各對(duì)信號(hào)線上的信號(hào)時(shí)序一致,并行設(shè)備需要嚴(yán)格同步時(shí)鐘信號(hào),或者采用額外的時(shí)鐘信號(hào)線。 通過串行通訊與并行通訊的對(duì)比,可以看出:串行通訊很簡(jiǎn)單,但是相對(duì)速度低;并行通訊比較復(fù)雜,但是相對(duì)速度高。更重要的是,串行線路僅使用一對(duì)信號(hào)線,線路成本低并且抗干擾能力強(qiáng),因此可以用在長(zhǎng)距離通訊上;而并行線路使用多對(duì)信號(hào)線(還不包括額外的控制線路),線路成本高并且抗干擾能力差,因此對(duì)通訊距離有非常嚴(yán)格的限制。歷史最早的計(jì)算機(jī)設(shè)備之間全部采用串行接口,比如硬盤接口、打印機(jī)接口、通訊端口等等。那時(shí)候都是分立元件的電路設(shè)計(jì),如果采用并行接口,元件的數(shù)量和占用的空間將成倍增長(zhǎng)。比如一個(gè)8bit并行線路的接口元件數(shù)量將是串行線路的8倍(你得為每根信號(hào)線配置一套接收電路)。這個(gè)時(shí)期的數(shù)據(jù)通訊只能是非常簡(jiǎn)單而低速的。 但是集成電路技術(shù)的出現(xiàn)帶來了一個(gè)轉(zhuǎn)變,當(dāng)大量元件可以集成到一個(gè)小小的芯片上時(shí),并行通訊變得廉價(jià)而方便了。不論是8bit、16bit還是更高位數(shù)的并行線路,只需要一個(gè)并行接口芯片就可以處理,這比一個(gè)處理串行通訊的芯片成本高不到哪里去。與串行通訊相比,并行通訊在同樣的工作頻率下,通訊速度就可以整倍提高。因此適應(yīng)了當(dāng)時(shí)計(jì)算機(jī)設(shè)備發(fā)展的需要,硬盤、打印機(jī)等速度較快的設(shè)備開始使用并行通訊,PATA、SCSI、Parallel Port成為最為流行的并行通訊接口,被大眾所熟知。不過并行線路固有的一些缺點(diǎn)仍然限制了并行通訊的應(yīng)用范圍,至于超高速通訊和長(zhǎng)距離通訊方面,由于線路成本比接口成本要重要得多,因此一直都是串行通訊的應(yīng)用領(lǐng)域。 除了并行通訊具有速度優(yōu)勢(shì)以外,串行通訊自身也有一個(gè)問題。在計(jì)算機(jī)內(nèi)部,數(shù)據(jù)往往都是并行方式傳送的,當(dāng)采用串行方式與外界通訊時(shí)必須經(jīng)過串/并轉(zhuǎn)換處理。在早期集成電路規(guī)模較小的時(shí)代,串/并轉(zhuǎn)換電路的處理能力十分有限,因此串行通訊的速度無法提高。隨著如今集成技術(shù)的發(fā)展,邏輯電路的集成能力大大提高,甚至超過了IO連接單元的集成水平,從而逐步解決了串/并轉(zhuǎn)換速度的限制。另一方面,現(xiàn)在集成邏輯處理電路的成本也比IO連接單元更便宜,因此串行通訊再次顯示出它的優(yōu)勢(shì)。如果說集成電路技術(shù)一度幫助并行通訊流行起來,那么現(xiàn)在的高度集成水平則幫助串行通訊重返主流應(yīng)用領(lǐng)域。轉(zhuǎn)載“玩轉(zhuǎn)單片機(jī)”

深圳市菲利盟電子技術(shù)有限公司

| 歡迎光臨 電子工程網(wǎng) (http://m.qingdxww.cn/) | Powered by Discuz! X3.4 |