博客

初入Verilog HDL /CPLD之管腳定義

|

剛剛買了塊FPGA/CPLD的板子,在家沒事的時候拿出來玩玩,大學的時候弄過點點VHDL,有點C語言的底子,看起來不是很難,弄的時候卻大傷腦筋了。

開始當然是從LED流水燈開始了,自己敲了遍程序,新建工程,編譯太多的警告,Pin Planer下隨便定義了一下引腳,下載程序后發現板子上除了LED燈,數碼管也亮了,菜鳥真傷不起,百X了一下, 管腳分配的幾種方法.

FPGA管腳分配文件保存方法

使用別人的工程時,有時找不到他的管腳文件,但可以把他已經綁定好的管腳保存下來,輸出到文件里。

方法一:

查看引腳綁定情況,quartus -> assignment -> Pins,打開FPGA引腳界面,在這個界面的菜單中可以保存引腳文件為csv格式(表格形式)和tcl格式。

步驟:File -> Export… -> 選擇保存名字和保存格式。

方法二:

直接輸出管腳配置,assignmengt -> Export assignmengt,可以保存配置為qsf格式,該格式可以用記事本查看,在該文件中同樣包含了引腳信息。注意:保存時會在原工程文件夾下新建一個文件夾。

至于元件的其它配置方式,可以在qsf文件和tcl文件中用語句來設置,也可以在Assignment -> device,界面中設置。

加載:

使用已經有的引腳文件時,在選項assignment -> Import assignment,中可以選擇要加載的引腳文件。此時,可以加載qsf 和 csv(或txt)文件。

保存的csv(txt)文件、qsf文件 和 tcl文件的區別:

csv(txt)文件:包含芯片所有管腳信息,包括分配的和未分配的;

qsf文件:包含管腳分配信息和芯片信息;

tcl文件:只包含已分配管腳信息。

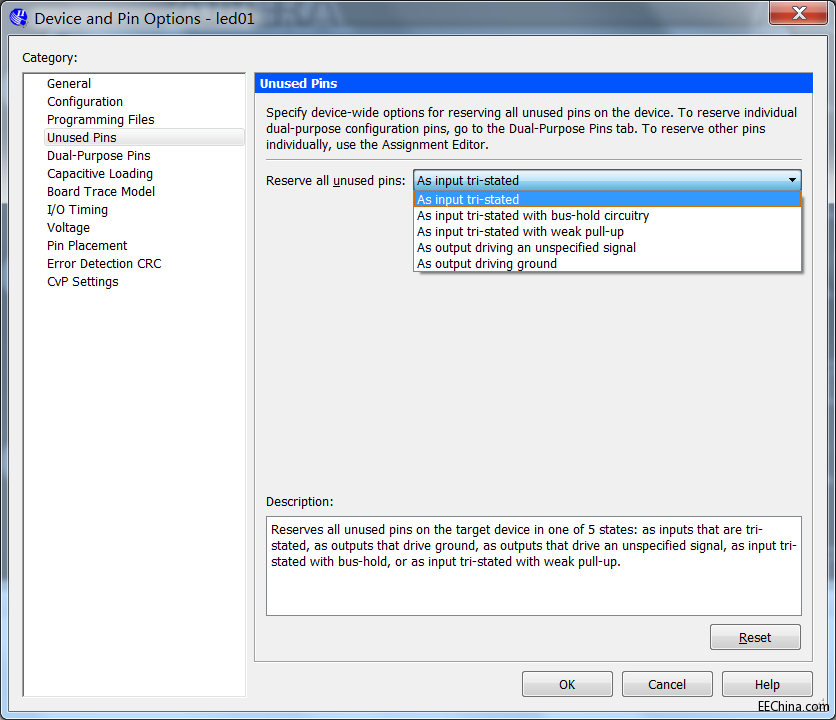

最后總結最重要的一點,就是沒有使用的IO一定要進行狀態的定義:

Assignment >> Device >>選擇Device and pins options >> unusedpin >>設置為Tri-stated(軟件設置有很多種可以選擇),再次重新編譯和下載,其他沒有用到的IO就不會出現其他不可預料的狀況了(我之前沒設置就導致使用開發板時,明明沒定義的數碼管IO卻把所有的都點亮了>=<)。